# Reconfigurable Low-Pass Filter for Analog Baseband of Bluetooth Low Energy and Biomedical Applications

# Ersin Alaybeyoğlu<sup>1,2</sup> 🝺, Hakan Kuntman<sup>2</sup> 🝺

<sup>1</sup>Department of Electrical and Electronics Engineering, Bartin University, Bartin, Turkey <sup>2</sup>Department of Electronics and Communications Engineering, Istanbul Technical University, Istanbul, Turkey

Cite this article as: Alaybeyoğlu E, Kuntman H. Reconfigurable Low-Pass Filter for Analog Baseband of Bluetooth Low Energy and Biomedical Applications. *Electrica*, 2021; 21(1): 142-150.

#### ABSTRACT

In this study, we proposed a low-pass filter that dissipated very low power with dynamic threshold metal–oxide–semiconductor technique for Bluetooth low energy and biomedical applications of new portable Internet-of-Things devices. The operating frequency of the designed low-pass filter is between 750 and 1 MHz to meet the baseband requirements of Bluetooth and filter biomedical signals. The circuit uses two supplies to develop the performance of the circuit. The core circuit of the OTA-C filter operates on the sub-threshold region with  $\pm$ 0.2-V supply voltage, whereas the supply voltage of the biasing circuit is 0.6 V. The power consumption of the designed filter is 0.34 nW at 750 Hz and 376 nW at 1 MHz. The performance of the designed circuit is tested in Cadence environment with TSMC 0.18- $\mu$ m technology.

Keywords: Biomedical applications, Operational Transconductance Amplifier (OTA), bluetooth low energy

#### Introduction

Multi-standard transceiver, which provides different standards in a single chip, should take into consideration various aspects in parallel and separate device-based solutions. Particularly, hardware sharing must be maximum between transceivers that support different standards to minimize both silicon area and static power consumption [1–5]. Some applications of Internet-of-Things (IoT) devices must provide the standards from biomedical acquisition systems to multi-standard wireless receivers [6–8]. However, even for a single application, such as Bluetooth, some circuit designs need to be reconfigurable. For example, the cut-off frequency of the analog baseband should be programmable to 1, 2.2, and 11 MHz for Bluetooth, UMTS, and WLAN, respectively [4, 9]. Biomedical applications should also operate from <1 to 10 kHz [10].

Bluetooth technologies have been developed rapidly around the world since the release of Bluetooth 2.1+EDR in 2007. Since then, Bluetooth has been used in wireless high-quality music equipment, smartphone technologies, human-interface devices, and car convenience systems. The IEEE 802.15 Working Group of special industry group (SIG) has developed the Bluetooth, and the SIG manages Bluetooth v1.1 to v5.1 [11]. The SIG, in which they were focusing on data rate (BR/EDR) for the transfer of audio signals in the past, has united with the Wibree forum and launched Bluetooth low energy (LE) v.4.0 in 2010. SIG is also currently working hard to develop LE to meet the IoT demands, where intensive work is underway. For small and low-power devices in the IoT market, LE is the best solution. Bluetooth technology is also used in health care, proximity detection, indoor positioning systems, sports and fitness [11].

When considering the low energy obtained by methods such as energy harvesting, circuits such as filters and LNA with very low-power consumption designed for Bluetooth LE are important, in which they are used in communication required for IoT applications [12, 13].

To meet the wireless features of Bluetooth and biomedical applications, we designed a lowpass filter (LPF) with a wide range of settings based on  $G_m$ -C filter topology, which consumes very low power, suitable for Bluetooth LE and biomedical signal acquisition devices used in

**Corresponding Author:** Ersin Alaybeyoğlu

E-mail: ealaybeyoglu@bartin.edu.tr

Received: 24.06.2020

Accepted: 04.08.2020

DOI: 10.5152/electrica.2021.20064

Content of this journal is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License. IoT applications. To improve the performance of operational transconductance amplifiers (OTA) acting as  $G_m$  block, we used the cross-coupled transistors as the output stage of the OTA structure. However, we selected the supply voltage of the biasing transistors larger than the main circuit to increase the dynamic range of the design. The supply voltages of the core design and the biasing circuit are  $\pm 0.2$  and 0.6 V, respectively. To improve the performance of transistors, we implemented the designed circuit with dynamic threshold metal–oxide–semiconductor (DTMOS) technique in the sub-threshold region [14–16].

The rest of the paper is organized as follows. Section 2 gives the voltage mode  $G_m$ -C filter. Section 3 describes the CMOS realization of  $G_m$ -C filter and explains the importance of the dual supply. Section 4 illustrates the layout of the second-order Butterworth filter structure and gives the transient and AC analysis of the filter with the third-order intercept point (IIP3) and noise analysis; additionally, the performance of the designed filter is justified by comparing conventional designs. Section 5 concludes this paper.

#### Voltage Mode G\_-C Filter

If noise-filtering is incorporated into the biomedical signal acquisitions systems, the use of LPF and analog-to-digital conversion are indispensable. In CMOS technology, LPF designs operating in the deep sub-threshold region are preferred to minimize power consumption and silicon area and can also be used in Bluetooth LE designs [17–19].

$G_m$ -C topologies are useful in performing analog filters. When designing filters for a multi-standard signal acquisition system, the design of reconfigurable circuits is as important as low-power consumption. For several decades, the frequencies of interest may vary depending on the nature of different applications or physical signals. Thus, it is more economical to design and manufacture reconfigurable hardware that can meet different specifications. Among the various filter architectures,  $G_m$ -C filters have become popular choices in the design of continuous-time filters because of their easy adjustment capabilities and low-power consumption [17–22].

Generally,  $G_m$ -C designs consume low power and can be designed for low-frequency applications. It is possible to design a lower-power consuming OTA with small transconductance in weak inversion so that the capacitor used takes up less area on the chip [20–22].

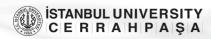

Figure 1 shows the structure of the implemented OTA-C filter. The transfer function of LPF is given in Equation (1) as follows:

$$\frac{V_{LP}}{V_{in}} = \frac{g_{m1}g_{m2}}{s^2 C_1 C_2 + s C_1 g_{m2} + g_{m1} g_{m2}} \tag{1}$$

where  $g_m$  denotes the transconductance of OTA.

Equations (2) and (3) give the resonance frequency ( $\omega_o$ ) and quality factor (Q), respectively.

$$\omega_0 = \sqrt{\frac{g_{m1}g_{m2}}{C_1 C_2}}$$

(2)

$$Q = \sqrt{\frac{C_2 g_{m1}}{C_1 g_{m2}}} \tag{3}$$

#### 3. CMOS Implementation of the Designed Filter

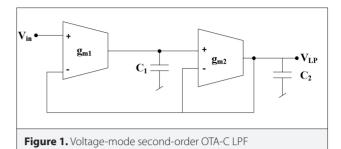

Figure 2 shows the CMOS implementation of LPF designed for analog baseband of Bluetooth LE and biomedical signal acquisition systems. The design of the proposed filter is implemented with 0.18-µm TSMC technology using DTMOS technique. The transistor aspect ratio of transistors in core design is 0.36 µm/0.36 µm, and the aspect ratio of the biasing transistors is 10 µm/2 µm. and are 10 kΩ, and C, and C, are 50fF.

In improving the performance of the MOS transistors with the same power dissipation, previous studies have investigated different techniques such as DTMOS [15, 23-25]. DTMOS shows high-current gain under the same supply voltage of standard CMOS transistor. The low-threshold characteristic of DTMOS increases the gain of transistors. In terms of power dissipation with the same gain, DTMOS is more useful in the design of analog circuits [26]. The realization of DTMOS is based on connecting the device gate and body, which changes dramatically the threshold voltage of the transistor using the relationship given in Equation (4). DTMOS has a higher transconductance than the standard CMOS transistor under the same  $V_{GS}$  voltage. The threshold voltage with  $V_{_{BS}} = 0$  is denoted by  $V_{_{th0}}$ ,  $\gamma$  and  $\varphi_{_F}$ are technology-dependent parameters having typical values of  $0.4/\sqrt{V}$  and 0.4V, respectively. Equation (5) gives the transconductance under the sub-threshold region.

$$|V_{th,p}| = |V_{th0,p}| + \gamma_p(\sqrt{|2\Phi_F| + V_{BS}} - \sqrt{|2\Phi_F|})$$

(4)

$$g_m = \frac{I_D}{nV_T} \tag{5}$$

In Figure 2, only the pMOS transistors are implemented by DT-MOS transistors because of the restriction of the double-well structure of the used 0.18-µm technology. The expensive triple well (deep *n*-well) technology is appropriate in designing both nMOS and pMOS transistors with DTMOS technique. Here, we used double-well technology to design the proposed filter because it is cheap.

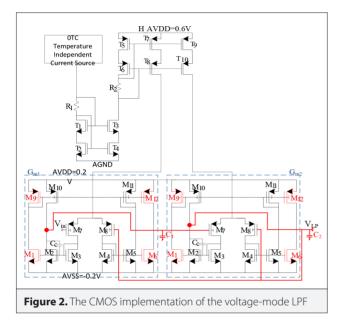

The conventional symmetrical OTA is modified with  $M_1$ ,  $M_6$ ,  $M_9$ , and  $M_{12}$  transistors to operate at ±0.2 V. Figure 3(a) shows the conventional symmetrical OTA.  $C_c$  (100 fF) is the compen-

sation capacitance. The voltage gain of the conventional symmetrical OTA denoted by  $A_{v_1}$  is represented in Equation (6), whereas  $A_{v_2}$  of the proposed circuit given in Figure 3(b) is changed to Equation (7).

$$A_{V1} \cong \frac{V_o}{V_{in}} = \frac{g_{m7,8}}{g_{m3.4}} \frac{g_{m2,10}}{g_{ds2.10}}$$

(6)

$$A_{V2} \cong \frac{V_o}{V_{in}} = \frac{g_{m7,8}}{g_{m3,4}} \frac{g_{m2,10}}{g_{m9}}$$

(7)

$g_{m_{3,4}}$  and  $g_{m_{7,8}}$  are constant.  $\Delta g_{m_{3,4}}=0$  and  $\Delta g_{m_{7,8}}=0$  because the current flowing through M<sub>3</sub>, M<sub>4</sub>, M<sub>7</sub>, and M<sub>8</sub> are constant. Thus, Equation (7) with the change in  $g_m$  represented as  $\Delta g_m$  can be rewritten in the following Equation (8).

$$A_{V2} \cong \frac{V_o}{V_{in}} = \frac{g_{m7,8}}{g_{m3,4}} \frac{(g_{m2,10} + \Delta g_{m2,10})}{(g_{m9} + \Delta g_{m9})}$$

(8)

In the design, transistors are biased in the sub-threshold region. Thus, the change in their transconductance, , and can be expressed in the following Equation (9).

$$\Delta g_{m2,10} = \frac{2\Delta I_{DS2,10}}{nV_T}, \Delta g_{m9} = \frac{2\Delta I_{DS9}}{nV_T}$$

(9)

$I_{DS9}$  is equal to  $I_{DS3,4}$  in the condition of the same ratio of  $M_3 - M_2$ and  $M_4 - M_5$ . Substituting Equation (9) into Equation (8) leads to Equation (10) [27].

and +0.2 V with unity feedback

**Figure 5.** The transconductance of the designed OTA according to the biasing currents

$$A_{V2} \cong \frac{V_o}{V_{in}} = \frac{g_{m7,8}}{g_{m3,4}} \frac{(g_{m2,10} + \frac{2\Delta I_{DS2,10}}{nV_T})}{(g_{m9} + \frac{2\Delta I_{DS9}}{nV_T})}$$

(10)

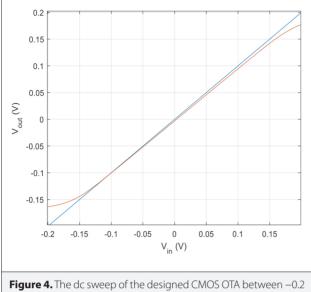

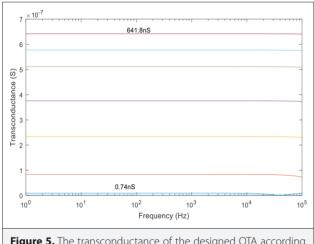

Figure 4 shows the dc sweep of the designed CMOS OTA between -0.2 and +0.2 V. Figure 5 shows the simulated transconductance of the designed OTA according to the biasing current. The transconductance of the proposed circuit is given in Equation (11). Table 1 shows the values of transconductance according to the biasing current.

$$\frac{I_o}{V_{in}} = \frac{g_{m7,8}}{g_{m3,4}} (g_{m2,10} + \frac{2\Delta I_{DS2,10}}{nV_T})$$

(11)

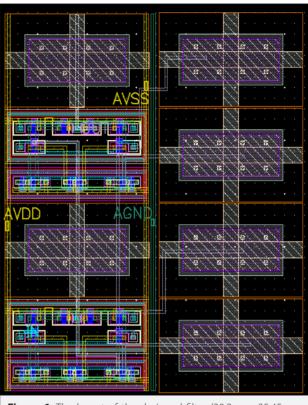

Figure 6. The layout of the designed filter (30.2  $\mu m \times 35.45 \ \mu m;$  0.00107  $mm^2)$

| Table 1. Biasing current versus transconduce | uctance |

|----------------------------------------------|---------|

|----------------------------------------------|---------|

| Biasing current (nA) | Transconductance (nS) |

|----------------------|-----------------------|

| 0.1                  | 0.74                  |

| 1                    | 9.3                   |

| 10                   | 83.2                  |

| 30                   | 233.9                 |

| 50                   | 375.4                 |

| 70                   | 511                   |

| 80                   | 576                   |

| 90                   | 641.8                 |

By adding  $M_{1'}$ ,  $M_{6'}$ ,  $M_{9'}$  and  $M_{12}$  transistors, we reduced  $G_m$  of OTA to support biomedical applications with Bluetooth LE in the same design. In the  $g_m$  reduction method, the second stage gain is minimized by decreasing the output high impedance. The simulated  $G_m$  in conventional design is obtained as 1.07 nS with 0.1 nA biasing current, whereas  $G_m$  of the proposed design is 0.745 nS with 0.1 nA.

We used two different supply voltages to improve the design's dynamic range. For example,  $T_8$  and  $T_{10}$  transistors cause the

| Table 2. Improvement in basic OTA performance quantities provided by different H_AVDD values |       |        |                |                 |          |

|----------------------------------------------------------------------------------------------|-------|--------|----------------|-----------------|----------|

| H_AVDD                                                                                       | THD   | Power  | Noise @ 10 kHz | <i>f</i> (-3dB) | Gm       |

| 0.4V                                                                                         | 9.41% | 109 nW | 1.01 µV/√Hz    | 276 kHz         | 213.2 nS |

| 0.6V                                                                                         | 4.96% | 115 nW | 1 µV/√Hz       | 304 kHz         | 233.9 nS |

MHz for 376-nA biasing current of both OTA)

voltage to decrease to 2 V<sub>ON</sub> at the output, assuming that they operate in the saturation region. V<sub>ON</sub> denotes the minimum voltage of saturation as  $V_{ON} = V_{GS} - V_{TH}$ .

$2\ V_{_{ON}}$  is not important because MOSFET is performed in the sub-threshold region; however, a larger value must be used

for the supply voltage of the biasing transistors to improve the dynamic range. Although MOSFET behaves like BJT in the sub-threshold region, the drain current is still depended [26] to the  $(V_{GS} - V_{tr})$ , as given in Equation (12).

$$I_D = C_{OX} \cdot \mu_{eff} \frac{W}{L} \cdot n \cdot V_T^2 \cdot e^{(v_{GS} - v_{th})/nV_T}$$

(12)

In the design, the headroom is enlarged by transistors operating in the sub-threshold region and using two different supply voltages. The voltage drop is approximately simulated as 0.05 V given in Figure 4 for 0.6-V supply voltage of biasing transistors.

# 4. Layout and its Simulations

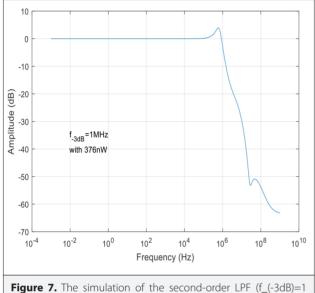

Figure 6 shows the layout of the designed circuit. The core occupation areas of the designed circuit are  $30.2 \ \mu m \times 35.45 \ \mu m$ and  $0.00107 \ mm^2$ . Figure 7 shows the post-layout simulation of the second-order LPF. The cut-off frequency of the designed filter is 1 MHz for the 90-nA biasing current of both OTAs.

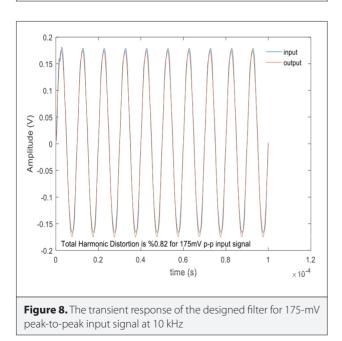

Figure 8 shows the transient response for 175-mV peak-to-peak input signal at 10-kHz frequency. The total harmonic distortion is 0.82%. The boundary for the input level of the design is 175 mV. The designed filter has low distortion for the low-input level. The big value selection of the biasing circuit's supply improves the input common-mode range of the designed filter.

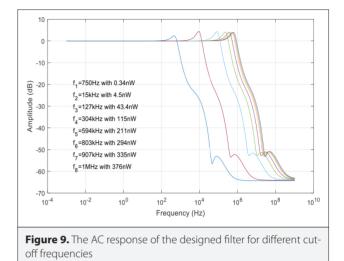

The cut-off frequency of the designed filter can be programmable with the biasing current, as shown in Figure 9. The maximum power dissipation of the designed circuit is 376 nW at 1-MHz cut-off

Table 3. Comparison of the designed filter with state of the art

| Specification                                                        | [9]              | [29]           | [30]               | [31]              | [13]             | [7]                | This work              |

|----------------------------------------------------------------------|------------------|----------------|--------------------|-------------------|------------------|--------------------|------------------------|

| Technique                                                            | Gm–C             | Active RC      | Active RC          | Active RC+DT      | Active RC        | Gm–C               | Gm–C                   |

| Technology (µm)                                                      | 0.18             | 0.12           | 0.13               | 0.065             | 0.18             | 0.090              | 0.18                   |

| Order                                                                | 3                | 5              | 5                  | 4                 | 4                | 4                  | 2                      |

| Bandwidth (MHz)                                                      | 0.5              | 5              | 19.7               | 10                | 0.6              | 12                 | 1                      |

| DC gain (dB)                                                         | 0                | 0              | 2                  | 0                 | 10               | 0                  | 0                      |

| Input noise                                                          | 425              | 140            | 30                 | 22.8              | 126              | 293.6              | 216.3                  |

| IIP3 (dBm)                                                           | 22.3             | 20             | 18.3               | 11                | 25               | 28                 | 18.7                   |

| SFDR (dB)                                                            | 57.3             | 73             | 69                 | 58                | 65.6             | NA                 | NA                     |

| Power @ VDD                                                          | 4.1 m @<br>1.2 V | 6.1 m @<br>1 V | 11.25 m @<br>1.5 V | 10.8 m @<br>1.8 V | 0.5 m @<br>1.8 V | 11.83 m @<br>1.2 V | 0.34 nW @<br>0.4–0.6 V |

| Chip area (mm <sup>2</sup> )                                         | 0.23             | 0.25           | 0.2                | 0.75              | 0.14             | NA                 | 0.00107                |

| FoM ( $\begin{array}{c} W \times mm^2 \\ dBm \times H \end{array}$ ) | 28.1p            | 3.05p          | 1.24p              | 3.92p             | 33.3p            | NA                 | 1.28f                  |

frequency, whereas the minimum power dissipation is 0.34 nW. The operation of the designed filter is appropriate to Bluetooth applications and biomedical applications because of the need for low-power design of biomedical circuits and Bluetooth LE.

Table 2 shows the performance comparison of dual supply design for two different H\_AVDD values at 30-nA biasing current of  $I_{B}$ . The implementation of a double supply decreases the total harmonic distortion of the designed filter. Furthermore, the cut-off frequency and  $G_{m}$  of the designed filter are increased by the proposed technique. By increasing the supply of the biasing circuit from 0.4V to 0.6V, we increased the  $G_{m}$  of OTAs for 30-nA tail current from 213.2 to 233.9 nS, thus increasing the cut-off frequency of the designed circuit from 276 to 304 kHz. Although the proposed method improved circuit performance by 15%–20%, power consumption increased by only 5%. It may seem like a disadvantage to obtain two different supply voltages in the circuit. However, AVDD can be easily achieved using asymmetrical supply.

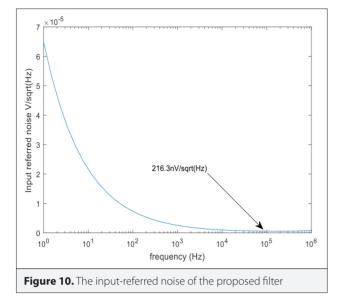

Input referred noise of the designed filter is 216.3 nV/sqrt(Hz), as shown in Figure 10.

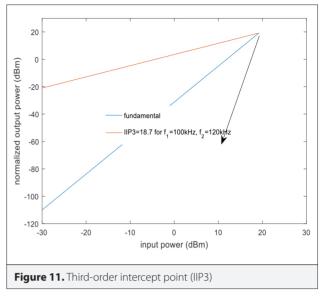

The IIP3 of the proposed filter is 18.7 dBm, as shown in Figure 11. IIP3 is tested for the 100 and 120 kHz tones. The required IIP3 value for the application of Bluetooth is 17.3 dBm [28].

Table 3 gives the comparison of the proposed circuit with conventional studies. The design is considered to be very successful when compared with the defined figure of merit (FoM) given in Equation (13). It has a very good performance compared with the recommended circuit, especially in terms of power consumption and core occupation area on the chip.

$$FoM = \frac{power \ x \ area}{order \ x \ IIP3 \ x \ bandwidth}$$

(13)

## Conclusions

This study proposed OTA-C filter for the baseband of Bluetooth LE and biomedical signal acquisition systems with DTMOS technique. The filter is designed with OTA-C filter topology with dual supply voltage:  $\pm 0.2$  V (core circuit) and  $\pm 0.6$  V (biasing circuit). We investigated a new implementation for the output stage of the symmetrical OTA. The input-referred noise of the designed filter is 216.3 nV/sqrt(Hz), and IIP3 of the designed filter is considered to be very efficient. Simulations are performed in Cadence environment with 0.18-µm TSMC technology.

Peer-review: Externally peer-reviewed.

Conflict of Interest: The authors have no conflicts of interest to declare.

Financial Disclosure: The authors declared that the study has received no financial support.

#### References

- A. Baschirotto, R. Castello, F. Campi, G. Cesura, M. Toma, R. Guerrieri, R. Lodi, L. Lavagno, P. Malcovati, "Baseband analog front-end and digital back-end for reconfigurable multi-standard terminals", IEEE Circuits Syst. Mag., vol. 6, no. 1, pp. 8-26, 2006. [Crossref]

- R. Bagheri, A. Mirzaei, S. Chehrazi, M. Heidari, M. Lee, M. Mikhemar, W. Tang, A. Abidi, "An 800MHz to 5GHz software-defined radio receiver in 90nm CMOS," in 2006 IEEE International Solid State Circuits Conference-Digest of Technical Papers, San Francisco, pp. 1932-1941, 2006. [Crossref]

- F. Agnelli, G. Albasini, I. Bietti, A. Gnudi, A. Lacaita, D. Manstretta, R. Rovatti, E. Sacchi, P. Savazzi, F. Svelto, E. Temporiti, S. Vitali and R. Castello, "Wireless multi-standard terminals: System analysis and design of a reconfigurable RF front-end", IEEE Circuits Syst. Mag., vol. 6, no. 1, pp. 38-57, 2006. [Crossref]

- S. D'Amico, A. Baschirotto, M. De Matteis, N. Ghittori, A. Vigna, P. Malcovati, "A CMOS 5 nV/-\/VHz 74-dB-gain-range 82-dB-DR multistandard baseband chain for bluetooth, UMTS, and WLAN", IEEE J. Solid-State Circuits, vol. 43, no. 7, pp. 1534-1541, 2008. [Crossref]

- M. B. Elamien, S. A. Mahmoud, "OTA-based switchable gain and order multi-standard receiver analog baseband chain", AEU - Int. J. Electron. Commun., vol. 106, pp. 1-11, 2019. [Crossref]

- A. A. Alhammadi, T. B. Nazzal, S. A. Mahmoud, "A CMOS EEG detection system with a configurable analog front-end architecture", Analog Integr. Circuits Signal Process., vol. 89, no. 1, pp. 151-176, 2016. [Crossref]

- J. R. M. Krishna, T. Laxminidhi, "Widely tunable low-pass gm C filter for biomedical applications", IET Circuits, Devices Syst., vol. 13, no. 2, pp. 239-244, 2019. [Crossref]

- M. B. Elamien, S. A. Mahmoud, "An 114 Hz-12 MHz digitally controlled lowpass filter for biomedical and wireless applications", IET Circuits, Devices Syst., vol. 12, no. 5, pp. 606-614, 2018. [Crossref]

- T. Y. Lo, C. C. Hung, M. Ismail, "A wide tuning range GmC filter for multi-mode CMOS direct-conversion wireless receivers", IEEE J. Solid-State Circuits, vol. 44, no. 9, pp. 2515-2524, 2009. [Crossref]

- R. R. Harrison, "A Versatile Integrated Circuit for the Acquisition of Biopotentials," in 2007 IEEE Custom Integrated Circuits Conference, San Jose, pp. 115-122, 2007. [Crossref]

- J. Lee, "Reconnection Establishment Scheme based on Energy Detection for Pre-paged Bluetooth BR/EDR Device", IEEE Internet Things J., vol. 7, no. 1, pp. 88-98, 2019. [Crossref]

- M. Alhawari, B. Mohammad, H. Saleh, M. Ismail, "A survey of thermal energy harvesting techniques and interface circuitry," in 2013 IEEE 20th International Conference on Electronics, Circuits, and Systems, Abu Dhabi, pp. 381-384, 2013. [Crossref]

- A. Rasekh, M. Sharif Bakhtiar, "Design of Low-Power Low-Area Tunable Active RC Filters", IEEE Trans. Circuits Syst. II Express Briefs, vol. 65, no. 1, pp. 6-10, 2017. [Crossref]

- H. F. Achigui, C. J. B. Fayomi, M. Sawan, PMC-Sierra, "1-V DT-MOS-based class-AB operational amplifier: Implementation and experimental results", IEEE J. Solid-State Circuits, vol. 41, no. 11, pp. 2440-2448, 2006. [Crossref]

- A. Uygur, B. Metin, H. Kuntman, O. Cicekoglu, "Current mode MOS-FET-only third order Butterworth low pass filter with DTMOS tuning technique", Analog Integr. Circuits Signal Process., vol. 89, no. 3, pp. 645-654, 2016. [Crossref]

- E. Alaybeyoğlu, H. Kuntman, "Capacitor multiplier with high multiplication factor for integrated low pass filter of biomedical applications using DTMOS technique", AEU - Int. J. Electron. Commun., vol. 107, pp. 291-297, 2019. [Crossref]

- S. M. A. Zanjani, M. Dousti, M. Dolatshahi, "Inverter-based, low-power and low-voltage, new mixed-mode Gm-C filter in subthreshold CNTFET technology", IET Circuits, Devices Syst., vol. 12, no. 6, pp. 681-688, 2018. [Crossref]

- Y. Lee, C. J. Cheng, "Systematic design and modeling of a OTA-C filter for portable ECG detection", IEEE Trans. Biomed. Circuits Syst., vol. 3, no. 1, pp. 53-64, 2009. [Crossref]

- S. Thanapitak, C. Sawigun, "A subthreshold buffer-based biquadratic cell and its application to biopotential filter design", IEEE Trans. Circuits Syst. I Regul. Pap., vol. 65, no. 9, pp. 2774-2783, 2018. [Crossref]

- S. Y. Lee, C. P. Wang, Y. S. Chu, "Low-Voltage OTA-C Filter with an Area- and Power-Efficient OTA for Biosignal Sensor Applications", IEEE Trans. Biomed. Circuits Syst., vol. 13, no. 1, pp. 56-67, 2019. [Crossref]

- C. Y. Sun, S. Y. Lee, "A Fifth-Order Butterworth OTA-C LPF with Multiple-Output Differential-Input OTA for ECG Applications", IEEE Trans. Circuits Syst. II Express Briefs, vol. 65, no. 4, pp. 421-425, 2018. [Crossref]

- Sheng-Yu Peng, Yu-Hsien Lee, Tzu-Yun Wang, Hui-Chun Huang, Min-Rui Lai, Chiang-Hsi Lee, Li-Han Liu, "A Power-Efficient Reconfigurable OTA-C Filter for Low-Frequency Biomedical Applications", IEEE Trans. Circuits Syst. I Regul. Pap., vol. 65, no. 2, pp. 543-555, 2018. [Crossref]

- 23. A. Uygur, H. Kuntman, "DTMOS-based 0.4 V ultra low-voltage low-power VDTA design and its application to EEG data processing", Radioengineering, vol. 22, no. 2, pp. 458-466, 2013.

- 24. S. S. Rout, S. Acharya, K. Sethi, "A low phase noise gm-boosted DTMOS VCO design in 180 nm CMOS technology", Karbala Int. J. Mod. Sci., vol. 4, no. 2, pp. 228-236, 2018. [Crossref]

- P. Kalekar, P. Vernekar, V. M. H. Vasantha, Y. B. N. Kumar, E. Bonizzoni, "A 0.5 v Low Power DTMOS OTA-C Filter for ECG Sensing Applications," in 2018 IEEE SENSORS, New Delhi, pp. 1-4, 2018. [Crossref]

- 26. C. Tsividis, Y. McAndrew, "Operation and Modeling of the MOS Transistor", Oxford Univ. Press, 2011.

- H. Liu, X. Zhu, C. C. Boon, X. He, "Cell-based variable-gain amplifiers with accurate dB-linear characteristic in 0.18 μm CMOS technology", IEEE J. Solid-State Circuits, vol. 50, no. 2, pp. 586-596, 2015. [Crossref]

- V. Giannini, J. Craninckx, S. D'Amico, A. Baschirotto, "Flexible baseband analog circuits for software-defined radio front-ends", IEEE J. Solid-State Circuits, vol. 42, no. 7, pp. 1501-1512, 2007. [Crossref]

- 29. V. Athanasios, Vasilopoulos Georgios, T. Gerasimos, P. Yannis, "A Low-Power Wideband Reconfigurable Integrated Active-RC Filter With 73 dB SFDR", IEEE J. Solid-State Circuits, vol. 41, no. 9, pp. 1997-2008, 2006. [Crossref]

- L. Ye, C. Shi, H. Liao, R. Huang, Y. Wang, "Highly Power-Efficient Active-RC Filters With Wide Bandwidth-Range Using", vol. 60, no. 1, pp. 95-107, 2013. [Crossref]

- S. H. Shin, S. J. Kweon, S. H. Jo, Y. C. Choi, S. Lee, H. J. Yoo, "A 0.7-MHz-10-MHz CT+ DT hybrid baseband chain with improved passband flatness for LTE application", IEEE Trans. Circuits Syst. I Regul. Pap., vol. 62, no. 1, pp. 244-253, 2015. [Crossref]

Ersin Alaybeyoğlu was born in Kastamonu, Turkey, in 1986. He received the B.Sc. degree in electrical and electronics engineering from the Hacettepe University, Ankara, Turkey, in 2010, and the M.Sc. and the Ph.D. degree in electronics & communication engineering, from the İstanbul Technical University, Turkey, in 2013 and 2017, respectively. His research interests cover analog circuit design, anolog filters & oscillators, digital circuit design, reconfigurable electronic circuit design and semiconductor devices. During his Ph.D., he worked on development and design of reconfigurable analog filters, cell-based variable transconductance amplifier and its applications of multi-standard transceivers and secure communications. Recently, his research focuses on the design of both Nyquist-rate and oversampled A/D converters, capacitor multipliers and digital electronic design. Dr. Alaybeyoğlu worked at Istanbul Technical University as research assistant between 2012 and 2016. Now, he is working in the department of the electrical and electronics engineering as assistant professor, Bartın University, Bartın, Turkey.

Hakan Kuntman received his B.Sc., M.Sc. and Ph.D. degrees from Istanbul Technical University in 1974, 1977 and 1982, respectively. In 1974 he joined the Electronics and Communication Engineering Department of Istanbul Technical University. Since 1993 he is a professor of electronics in the same department (retired, 2016). His research interest includes design of electronic circuits, modeling of electron devices and electronic systems, active filters, design of analog IC topologies. Dr. Kuntman has authored many publications on modelling and simulation of electron devices and electronic circuits for computer-aided design, analog VLSI design and active circuit design. He is the author or the co-author of 129 journal papers published or accepted for publishing in international journals, 179 conference papers presented or accepted for presentation in international conferences, 161 Turkish conference papers presented in national conferences and 10 books related to the above mentioned areas. He advised and completed the work of 15 Ph.D. students and 44 M.Sc students. Dr. Kuntman is a member of the Chamber of Turkish Electrical Engineers (EMO).

From 2001 to 2004 he acted as the Head of the Electronics and Communication Engineering Department, from 2004 to 2010 he was the Dean of Electrical & Elecronics Engineering Faculty of Istanbul Technical University, Furthermore, Dr. Kuntman is one of the founders of the ELECO conferences and acted as the Conference Chairman several times.